| Getting Started |   |

根軌跡の設計

設計規範をベースにした設計手法の一つは、根軌跡による設計です。このアプローチは、根軌跡図上で、極と零点を操作することにより、設計を繰り返し行うことを含んでいます。

1.5 -------------------- s^2 + 14.03 s + 40.3

補償器のゲインの変更

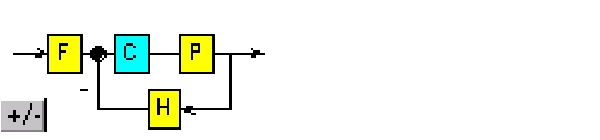

最も簡単なアプローチは、補償器のゲインの変更です。デフォルトで、SISO設計ツールは、根軌跡設計用のフィードバック構造はつぎのように考えています。

F、H、Cのデフォルト値は1です。DCモータプラントをインポートしているので、Pはこの構造を表わしています。

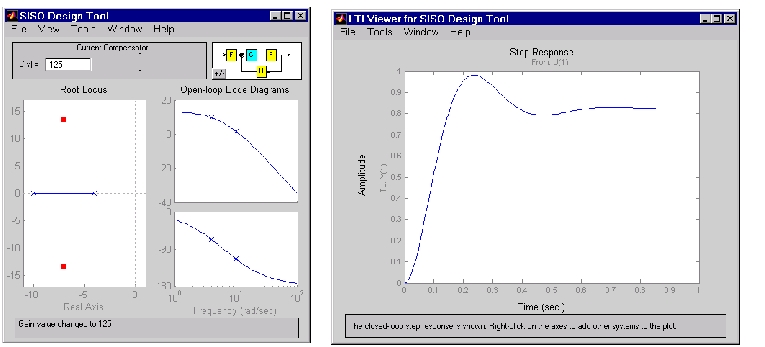

SISO設計ツールのC(s)フィールドのゲインを125(デフォルトは1)に設定しましょう。これにより、表示されるSISO設計ツールとLTI Viewer Step応答も変化します。

図 4-4:補償器のゲインを125にした時のDCモータの根軌跡、Bode線図、Step応答図

Step応答は、定常状態偏差と立ち上がり時間が改良されていることを示しますが、オーバーシュートがまだ、10%存在していることを示しています。

リードネットワークの付加

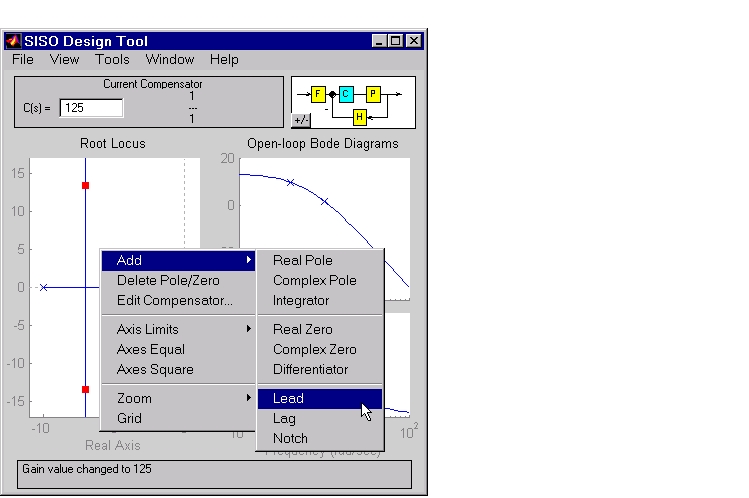

このことを改良する可能な解は、補償器にリードネットワークを付加することです。これを行うためには、マウスを根軌跡プロット領域に移動し、右クリックを行います。これにより、根軌跡設計用のオプションメニューがオープンします。付加(Add)メニューアイテムのリードネットワーク(Lead Network)を選択します。ユーザのSISO設計ツールは、つぎのようになります。

図 4-5:右クリックメニューを使って、DCモータ補償器にリードネットワークを付加

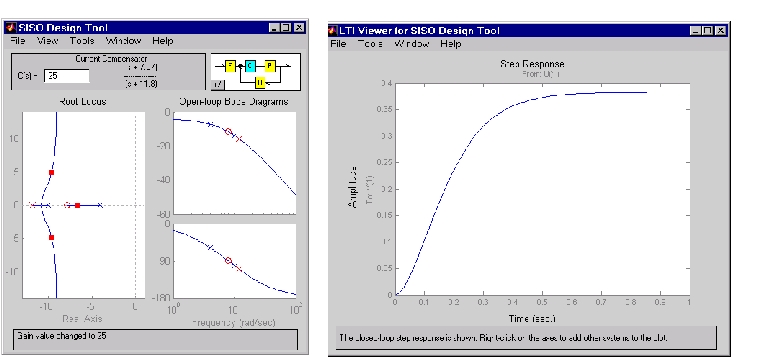

リードネットワークを選択すると、カーソルは、赤の'x'に変更します。実軸上にこの'x'を配置し、最も右側に位置する極の左をクリックします。また、補償器のゲインを25に変更します。SISO設計ツールとLTI Viewerは、つぎのような図を示します。

図 4-6:リードネットワークをもつDCモータの根軌跡、Step応答、Impulse応答

Step応答図は、立ち上がり時間は約0.34秒、整定時間が約0.34秒を示しています。これは、DCモータの性能規範を満足しています。定常状態偏差は、最終値が約0.4 rad/secであるので、まだ、高い値を示しています。それで、さらに作業を続けます。

ラグネットワークの付加

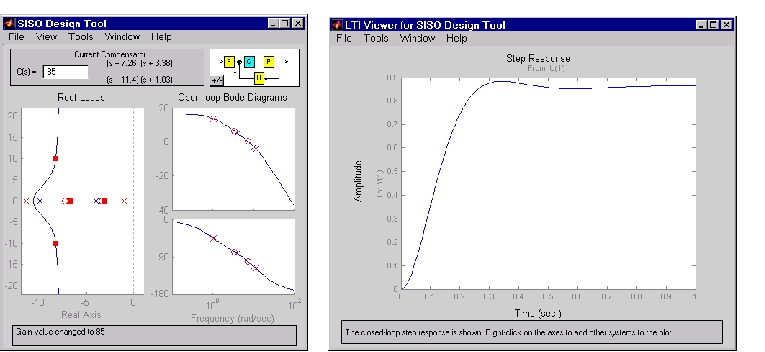

定常状態偏差を減らすために、もう一つの方法は、ラグネットワークを付加することです。手順は、リードネットワークと同じです。根軌跡図の中で、ユーザのマウスの右ボタンをクリックし、メニューリストをオープンします。メニューから付加(Add)とラグネットワーク(Rag Network)を選択します。根軌跡図の実軸上の-1の付近に赤の'x'印を配置します。補償器のゲインC(s)を85にすると、SISO設計ツールとLTI Viewerの図はつぎのようになります。

図 4-7:リードネットワークとラグネットワークをもつDCモータの根軌跡、Bode線図、Step応答図

Step応答図より、立ち上がり時間は約0.22秒、整定時間は約0.27秒、定常状態偏差は約12%であることがわかります。そして、オーバシュートは約3%です。設計は、この議論の最初に設定した設計規範を満足しています。

| SISO設計ツールのオープン | 周波数応答設計 |  |