Equation (5.22) - Transfer function for the variation of the clamp voltage in response to direct current injection in the clamp capacitor: the transfer function describing the response of the clamp voltage control system to a variation of the net current injected in the clamp capacitor can be obtained, according to the principle of superposition, by neglecting the clamp voltage reference input in Fig. III.1 and taking the disturbance input  $\Delta I_c^d$  as the main system input. The resulting transfer function can be written as:

$$\frac{\Delta V_c(s)}{\Delta I_c^d(s)} = \frac{G_{clamp}(s)}{1 + G_{PI}(s) \cdot G_{clamp}(s)} = \frac{\left(\frac{1}{sC_c}\right)}{1 + k_p \left(1 + \frac{1}{sT_i}\right) \left(\frac{1}{sC_c}\right)}$$

If this transfer function is reduced to the standard form, then equation (5.22) is obtained:

$$\frac{\Delta V_c(s)}{\Delta I_c^d(s)} = \frac{sT_i/k_p}{1+sT_i+s^2\frac{T_iC_c}{k_p}}$$

| <ul> <li>[85] D.S. Schramm, B.W. Williams and T.C. Green</li> <li>Optimum Commutation-Current Profile on Torque Linearization of Switched Reluc-<br/>tance Motors</li> <li>ICEM '92 Manchester Conference Proceedings, pp. 484-488, September 1992</li> </ul> |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>[86] James M. Simonelli and David A. Torrey</li> <li>An Alternative Bus Clamp for Resonant DC-Link Converters</li> <li>IEEE Transactions on Power Electronics, Vol. 9, No. 1, pp. 56-63, January 1994</li> </ul>                                     |

| <ul> <li>[87] G. Skibinski, J. Pankau</li> <li>Use of Multi Layer Ceramic (MLC) Capacitors in High Power Converters</li> <li>IEEE/IAS '96 Annual Meeting Conference Records, Vol. 3, pp. 1319-1926, Oct. 1996</li> </ul>                                      |

| [88] M.C. Smit, J.A. Ferreira, J.D. van Wyk and M.F.K. Holm<br>An Integrated Resonant DC-Link Converter, Using Planar Ceramic Capacitor Tech-<br>nology<br>PESC '94 Conference Proceedings, pp. 664-670, 1994                                                 |

| <ul> <li>[89] Rainer Sommer</li> <li><i>Der Active Clamped Resonant DC-Link Inverter - eine resonante Umrichterschaltung zur Frequenzumformung</i></li> <li>Doctoral Thesis, Fachbereich 12 Elektrotechnik, TechnischeUniversität Berlin, 1994</li> </ul>     |

| [90] M. Sprague and R. Krishnan<br>A High Performance DSP Based System Architecture for Motor Drive Control<br>PESC '94 Taipei Conference Records, Vol. 2, pp. 1257-1262, June 1994                                                                           |

| <ul> <li>[91] D. Staffiere and W.J. Sarjeant</li> <li>A Report on Capacitors</li> <li>APEC '96 New York Conference Records, Vol. 1, pp. 12-17, March 1996</li> </ul>                                                                                          |

| <ul> <li>[92] Ulrich Steiert</li> <li>Drehmomentsteuerung einer Reluktanzmaschine mit beidseitig ausgeprägten Polen<br/>und geringer Drehmomentwelligkeit</li> <li>Doctoral Thesis, Fakultät Elektrotechnik, Universität Karlsruhe, 1992</li> </ul>           |

| [93] Ulrich Steiert and H. Späth<br>Torque Control of the Doubly-Salient Reluctance Motor<br>ETEP Vol. 3, No. 4, July/August 1993                                                                                                                             |

| <ul> <li>[94] J.M. Stephenson and J. Corda<br/>Computation of Torque and Current in Doubly Salient Reluctance Motors from Non-<br/>linear Magnetisation Data<br/>IEE Proceedings, Vol. 126, Pt. B, No. 5, pp. 393-396, May 1979</li> </ul>                    |

| [95] Manfred Stiebler and Jie Ge<br>A Low Voltage Switched Reluctance Motor with Experimentally Optimized Control<br>ICEM'92 Manchester Conference Proceedings, pp. 532-536, September 1992.                                                                  |

| <ul> <li>[96] S.K. Sul and T.A. Lipo<br/>Field Oriented Control of an Induction Machine in a High Frequency Link Power<br/>System</li> <li>PESC '88 Kyoto Conference Proceedings, pp. 1084-1090, 1988</li> </ul>                                              |

|                                                                                                                                                                                                                                                               |

- [60] T.J.E. Miller

Switched Reluctance Motors and Their Control

Magna Physics Publishing and Clarendon Press Oxford, 1993, ISBN 0-19-859387-2

- [61] T.J.E. Miller and M. McGilp Nonlinear Theory of the Switched Reluctance Motor for Rapid Computer-Aided Design IEE Proceedings, Vol. 137, Pt. B, No. 6, pp.337-347, November 1990

- [62] T.J.E. Miller, P.G. Bower, R.C. Becerra and M. Ehsani Four-Quadrant Brushless Reluctance Motor Drive IEEE Conf. Power Electronics, CP-291, pp.273-276, July 1988

- [63] Sayeed Mir, Iqbal Husain and Malik E. Elbuluk Energy Efficient C-Dump Converters for Switched Reluctance Motors APEC '96 New York Conference Records, Vol. 2, pp. 968-973, March 1996

- [64] Mitsubishi Electric Co. Mitsubishi 3rd Generation IGBT- and Intelligent Power Modules Application Manual 1st Edition, 1994

- [65] Hassan H. Moghbelli and Muhammad H. Rashid *The Switched Reluctance Motor Drives: Characteristics and Performances* EPE '91 Firenze Conference Records, pp.1/398-1/403, 1991

- [66] Hassan H. Moghbelli, Gayle E. Adams and Richard G. Hoft *Performance of a 10-Hp Switched Reluctance Motor and Comparison with Induction Motors*  IEEE Transactions on Industry Applications, Vol. 27, No. 3, pp.531-538, May/June 1991

- [67] Ned Mohan, Tore M. Undeland and William P. Robbins Power Electronics - Converters, Applications and Design - Second Edition John Wiley & Sons, Inc., 1995, ISBN 0-471-30576-6

- [68] Y. Murai and T.A. Lipo High Frequency Series Resonant DC Link Power Conversion IEEE/IAS Annual Meeting Conference Records, pp. 772-779, 1988

- [69] J. Nicolai Simplified Electronics Bring the Switched-Reluctance Motor to the Mass Market EPE '95 Sevilla Conference Records, Vol. 3, pp. 903, 1995

- [70] J.G. O'Donovan, P.J. Roche, R.C. Kavanagh, M.G. Egan, J.M.D. Murphy Neural Network Based Torque Ripple Minimisation in a Switched Reluctance Motor IECON '94 Bologna Conference Proceedings, pp. 1226-1231, September 1994

- [71] S.-S. Park and T.A. Lipo

New Series Resonant Converter for Variable Reluctance Motor Drive

PESC '92 Toledo Conference Records, Vol. 2, pp. 833-838, June/July 1992

- [72] PCIM Magazine, Vol.9, No.3, 1997

| [35] Iqbal Husain and M. Ehsani<br>Torque Ripple Minimization in Switched Reluctance Motor Drives by PWM Curre<br>Control                                                                                                          | ent  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| IEEE Transactions on Power Electronics, Vol. 11, No. 1, pp. 83-88, January 1996                                                                                                                                                    | 5    |

| <ul> <li>[36] International Rectifier Corporation</li> <li><i>IGBT Designer's Manual</i></li> <li>1st Printing, 1994 (also under http://www.irf.com)</li> </ul>                                                                    |      |

| [37] Lutz Jänicke<br>Finite Elemente Methode mit adaptiver Netzgenerierung für die Berechnung dreid<br>mensionaler elektromagnetischer Felder<br>Doctoral Thesis, Fachbereich 12 Elektrotechnik, Technische Universität Berlin, 19 |      |

| [38] P.C. Kjaer, F. Blaabjerg, C. Cossar and T.J.E. Miller<br>Efficiency Optimisation in Current Controlled Variable-speed Switched Reluctant<br>Motor Drives<br>EPE '95 Sevilla Conference Proceedings, Vol. 3, pp. 741-747, 1995 | се   |

| [39] S. Kondo, S.H. Yang, S. Takizawa and F. Harashima<br>Resonant DC Link Dual Converter System for Motor Drives<br>IEEE/IAS Annual Meeting Conference Records, pp.789-794, 1991                                                  |      |

| [40] Ramu Krishnan and Peter N. Materu<br>Design of a Single-Switch-per-Phase Converter for Switched Reluctance Motor D<br>IEEE Transactions on Industrial Electronics, Vol. 37, No. 6, pp.469-476, Decemb<br>1990                 |      |

| [41] Ramu Krishnan and Peter N. Materu<br>Measurement and Instrumentation of a Switched Reluctance Motor<br>IEEE/IAS Annual Meeting Conference Records, pp.116-121, 1989                                                           |      |

| <ul> <li>[42] Ramu Krishnan and Peter N. Materu<br/>Analysis and Design of a New Converter Topology for Switched Reluctance Moto<br/>Drives<br/>IEEE/IAS Annual Meeting Conference Records, pp.1181-1185, 1989</li> </ul>          | r    |

| <ul> <li>[43] A. Kurnia, O.H. Stielau, G. Venkataramanan and D.M. Divan<br/>Loss Mechanisms in IGBTs under Zero Voltage Switching<br/>PESC '92 Toledo Conference Records, Vol. 2, pp. 1011-1017, June/July 1992</li> </ul>         |      |

| [44] J.S. Lai and B.K. Bose<br>An Improved Resonant DC Link Inverter for Induction Motor Drives<br>IEEE/IAS Annual Meeting Conference Records, pp. 742-748, 1988                                                                   |      |

| The first fundar Meeting Conference Records, pp. 712 716, 1966                                                                                                                                                                     |      |

| <ul> <li>[45] J.S. Lai and B.K. Bose</li> <li><i>High Frequency Quasi-Resonant DC Voltage Notching Inverter for AC Motor Dr</i><br/>IEEE/IAS Annual Meeting Conference Records, pp. 1202-1207, 1990</li> </ul>                     | ives |

| [45] J.S. Lai and B.K. Bose<br>High Frequency Quasi-Resonant DC Voltage Notching Inverter for AC Motor Dr                                                                                                                          | ives |

- [12] P.A. Dahono, H. Yamaguchi, Y. Sato and T. Kataoka A New Clamping Circuit to Reduce the Peak Voltage of Resonant DC Link Inverters IPEC '95 Yokohama Conference Records, pp. 1357-1361, 1995

- [13] R.W. De Doncker and J.P. Lyons *The Auxiliary Resonant Commutated Pole Converter* IEEE/IAS Annual Meeting Conference Records, pp. 1228-1235, 1990

- [14] R.W. De Doncker and J.P. Lyons *The Auxiliary Quasi-Resonant DC Link Inverter* IEEE/PESC '91 Conference Records, pp. 248-253, 1991

- [15] R.W. De Doncker and J.P. Lyons An Auxiliary Quasi-Resonant DC Link Inverter for Switched Reluctance Machines EPE '91 Firenze Conference Records, pp.4/018-4/023, 1991

- [16] R.W.A.A. De Doncker, T.M. Jahns, A.V. Radun, D.L. Watrous and V.A.K. Temple *Characteristics of MOS-Controlled Thyristors under Zero Voltage Soft-Switching Conditions*  IEEE Transactions on Industry Applications, Vol. 28, No. 2, pp. 387-394, March/April 1992

- [17] Deepakraj M. Divan *The Resonant DC Link Converter - A New Concept in Static Power Conversion*  IEEE Transactions on Industry Applications, Vol. 25, No. 2, pp. 317-325, March/April 1989

- [18] D.M. Divan, L. Malesani, P. Tenti, V. Toigo A Synchronized Resonant DC Link Converter for Soft-Switched PWM IEEE Transactions on Industry Applications, Vol. 29, No. 5, pp. 940-947, September/October 1993

- [19] Deepakraj M. Divan and Gary Skibinski Zero-Switching-Loss Inverters for High-Power Applications IEEE Transactions on Industry Applications, Vol. 25, No. 4, pp. 634-643, July/August 1989

- [20] D.M. Divan, G. Venkataramanan and R.W. De Doncker Design Methodologies for Soft Switched Inverters IEEE Transactions on Industry Applications, Vol. 29, No. 1, pp. 126-135, January/February 1993

- [21] M. Dehmlow, K. Heumann and R. Sommer *Resonant Inverter Systems for Drive Applications* EPE Journal, Vol. 2, No. 4, pp. 225-232, December 1992

# [22] Marvin Dehmlow Vergleichende Betrachtung unterschiedlicher resonanter Umrichtertopologien Doctoral Thesis, Fachbereich 12 Elektrotechnik, TechnischeUniversität Berlin, 1995

[23] Mehrdad Ehsani, James T. Bass, Timothy J.E. Miller and Robert L. Steigerwald Development of a Unipolar Converter for Variable Reluctance Motor Drives IEEE Transactions on Industry Applications, Vol. IA-23, No. 3, pp.545-553, May/June 1987 enables a considerable increase of the converter's power density, if the softswitching converter is operated with the same mean switching frequency and the same junction temperatures as the hard-switched one, because the softswitching converter would then require a much smaller heat sink. Alternatively, the soft-switching converter can be designed to operate at a mean switching frequency above the audible region, having roughly the same size as a hardswitching converter which operates with a five times lower mean switching frequency. The soft-switching converter also exhibits a lower rate of change of the voltage (dv/dt) at the switching instants, which is beneficial to the insulation of the machine windings and causes lower radiated EMI.

An experimental verification of the values which have been theoretically calculated in chapters 5 and 6 has not been possible with the test rig used and within the time frame of this work. Therefore, the following issues are suggested for further work:

- experimental determination of the maximum attainable power density of the SRM;

- redesign of the ACRDCL SR converter for maximum power density and evaluation of the actually attainable power density;

- experimental determination of the efficiency for the whole drive system for different operating conditions;

- development of an active input rectifier for the ACRDCL SR converter and of a single control unit for synchronized operation of the input and output stages.

vices employed. It depends only on the natural frequency of the resonant tank and on the current magnitude at the end of the boost phase, i.e. on the boost factor. The maximum value of dv/dt at the DC link voltage transitions can be found from equation (5.5) to be given by:

$$\left(\frac{dv}{dt}\right)_{max} = \omega_r \, V_s \, \sqrt{1.0 + k_b^2}.\tag{6.6}$$

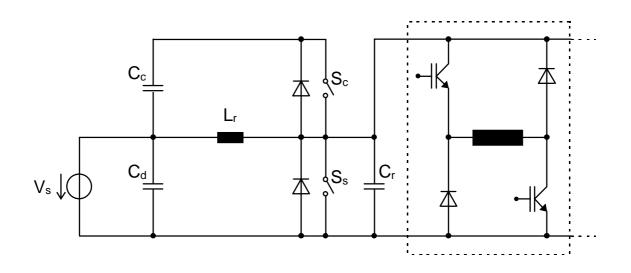

For a boost factor of 1.0 and a supply voltage of 500V, the maximum IEC specification would be met if the natural frequency of the resonant tank is lower than approximately 110 kHz, yielding a dc link frequency of approximately 70 kHz for a clamp factor of 1.5. The reduced dv/dt at the DC link transitions would also contribute to a reduction of the radiated EMI produced by the converter. With respect to the conducted EMI, if the DC link is fed by a diode rectifier with large DC link filter capacitance, no significant improvement can be expected, as has been verified in [22] for other soft-switching converter topologies. In this case, the large DC link filter capacitance practically decouple the input rectifier from the rest of the converter, so that it is relatively irrelevant if a hard- or a soft-switching converter is used in the output stage. However, the input current is very distorted, with poor power factor and high harmonic content if a diode rectifier is used in the input stage. As more and more rigorous standards for energy quality are prescribed, it is likely that diode input rectifiers become unacceptable due to input EMI filtering requirements. A potential substitute for diode rectifiers would be an active rectifier with control of the input current (Fig. 6.3). If this kind of rectifier is used with ACRDCL converters, then the zero-voltage notches of the resonant DC link can be also used to commutate the input switches under ZVS conditions. Additionally, regeneration is also possible with this topology.

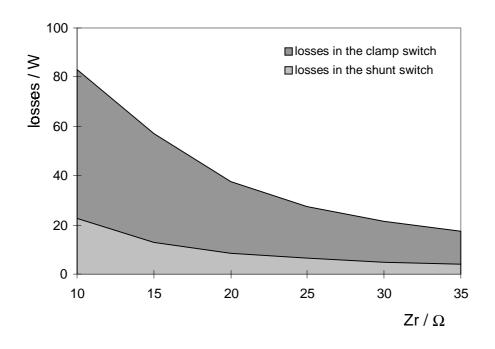

Fig. 6.2: Losses in the DC link switches versus characteristic impedance for fixed DC link frequency (80kHz).

The variation of the losses in the resonant inductor for different values of characteristic impedance is more difficult to predict. There are many possibilities for the construction of the resonant inductor, and each design parameter has a more or less strong impact on the inductor losses and on the inductor size. For instance, Sommer [89] has shown that the no-load losses in a resonant inductor with a ferrite core become lower if the inductance is increased. For a fixed natural frequency, the characteristic impedance of the resonant tank is directly proportional to the inductance. Therefore, the peak inductor current and the peak stored magnetic energy will be inversely proportional to the inductance:

$$I_{max} \propto \frac{V_s}{\omega_r L_r} \quad \therefore \quad E_{max} \propto 0.5 \left(\frac{V_s}{\omega_r}\right)^2 \frac{1}{L_r}.$$

(6.5)

If the magnetic core is designed to avoid saturation, i.e. for operation in the linear region, then the RMS value of the magnetic flux in the core will be approximately inversely proportional to  $\sqrt{L_r}$ , and the core losses will vary accordingly. If the core is not modified, then increasing the inductance by a factor

discrete power semiconductor devices and air-cooled heat sinks are used. The negative values in Table 6.3 indicate that the heat sink would have to be kept at a temperature below the ambient temperature, and this is not possible with natural air cooling. In contrast, it would be possible to implement the soft-switching converter using discrete devices for mean switching frequencies up to 30 kHz. Hence, operation of the soft-switching converter above the audible frequency region would be possible with a forced air-cooled heat sink, but the size of the heat sink would probably be very large. It is difficult to predict the size of the heat sink exactly, because the effective thermal resistance of an air-cooled heat sink depends on several factors, like the contact area between the power semiconductor devices ant the heat sink surface, the shape of the fins, the air flow speed between the fins and many others. Nevertheless, some typical values of volumetric thermal resistance for air-cooled heat sinks under different flow conditions are presented in Table 6.4, which has been taken from reference [49].

*Table 6.4: Volumetric thermal resistance*  $(cm^{3}K/W)$  *of air-cooled heat sinks.*

| flow condition (m/s) | volumetric thermal resistance (cm <sup>3</sup> K/W) |

|----------------------|-----------------------------------------------------|

| natural convection   | 500-800                                             |

| 1.0                  | 150-250                                             |

| 2.0                  | 80-150                                              |

| 5.0                  | 50-80                                               |

If power modules were used instead of discrete devices, it would be possible to operate the hard switched converter at a mean switching frequency above the audible region. However, it would require an air-cooled heat sink which would be twice as large as the one that would be required to operate the softswitching converter at the same frequency. In this case, there would be a significant gain in power density if soft switching is used, because the heat sink itself represents a considerable part of the total converter's weight. In this design The switching losses for the soft-switching case in Table 6.2 have been calculated under the assumption that the ZVS losses in IGBTs are 1/6 of the hardswitching losses. In fact, the ZVS losses depend strongly on the rate of rise of the collector-emitter voltage at turn-off. This in turn depends on the natural frequency of the resonant tank and on the "trip" current level at which the shunt switch in the DC link is turned off. As already mentioned above, the switching loss reduction rate of approximately 1/6 has been experimentally determined for second-generation IGBTs from both (low saturation and fast switching) types and is valid for a natural frequency of approximately 80kHz, which yields a DC link frequency of approximately 50 kHz if the clamp factor is 1.5. In the case where the sampling frequency (DC link frequency in the softswitched converter) is 100 kHz, the required resonant frequency is approximately 150 kHz. In this case, the switching loss reduction is somewhat lower and lies between 1/5 and 1/4 for second-generation fast-switching IGBT devices. In order to evaluate the influence of the loss reduction due to softswitching on the converter size, some design options are discussed next.

### 6.3 Converter sizing

If one wishes to construct SR converter like the one that has been simulated, there are two possibilities for the choice of the IGBT devices. First, one may choose to construct the converter using discrete components. Suitable IGBTs and diodes for the power level in question are encapsulated in a TO-247 package, which weights just 6g and can dissipate up to 78W at a maximum case temperature of 100°C (considering a maximum junction temperature of 150°C). The total weight of the semiconductor devices in the output section would be then just 72g. Alternatively, one may use chopper power modules consisting of one IGBT and one diode, which weigh 150g and can dissipate up to 180W under the same conditions as above, because they have a better thermal interface to the heat sink. In this case the total weight of the semiconductor devices would be 900g. For the purpose of comparing the resultant heat sink sizes in each case, the required thermal resistance of the heat sink to ambient

The conduction and the switching losses in the IGBT devices have been calculated using the conduction and the switching models presented in [36], for a 1200V, 50A fast switching IGBT. The losses due to reverse recovery and the switching losses in the diodes have been neglected. The conduction losses in the diodes have been calculated by interpolation of the forward voltage drop versus forward current characteristics from the diode's data sheet. The model equations are summarized as follows:

IGBT on-state voltage drop:  $v_{CE} = (V_0 + V_1 T) + (a_0 + a_1 T) \cdot i_c^{(b_0 + b_1 T)};$  (6.1)

IGBT turn-on energy loss:

$$E_{on} = (h_0 + h_1 T) \cdot i_c^{(k_0 + k_1 T)};$$

(6.2)

IGBT turn-off energy loss:

$$E_{off} = (m_0 + m_1 T) \cdot i_c^{(n_0 + n_1 T)};$$

(6.3)

diode forward voltage drop:

$$v_f = V_F + c \cdot i_f^d$$

; (6.4)

where *T* is the junction temperature in °C. The diode model parameters have been calculated from data sheet characteristics for a fixed junction temperature of  $100^{\circ}$ C.

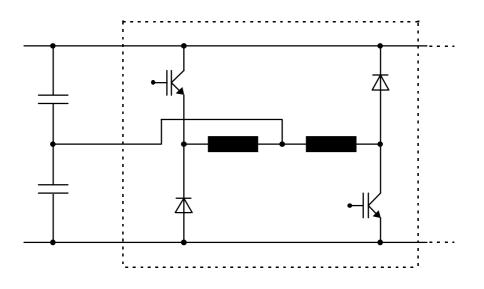

If the soft-chopping control method is used, the partitioning of the total power losses in conduction and switching losses is quite different in the soft-chopped SRM converter, when compared to a converter for induction motor drives. This is due to the fact that only the upper switches are pulsed in the soft-chopping SRM converter. The lower switches are turned on and off only one time for each phase current pulse. As a result, the lower switches will exhibit practically only conduction losses, while the switching losses in the upper switches can be higher than the conduction losses (see Table 6.1). The relative distribution of the loss components on the semiconductor devices is shown in Table 6.2 for mean switching frequencies of 7.5, 15 and 30 kHz, which correspond to the sampling frequencies of 25, 50 and 100 kHz, respectively.

| fs<br>kHz | $\overline{f}_{sw}$<br>kHz | P <sub>sh</sub><br>W | P <sub>sl</sub><br>W | P <sub>dh</sub><br>W | $P_{dl}$ $W$ | P <sub>sw</sub><br>W | P <sub>total</sub><br>W |

|-----------|----------------------------|----------------------|----------------------|----------------------|--------------|----------------------|-------------------------|

| 20        | 6                          | 33.5                 | 49.2                 | 6.3                  | 21.2         | 21.8                 | 132.0                   |

| 25        | 7.5                        | 33.1                 | 49.6                 | 5.9                  | 21.6         | 27.0                 | 137.2                   |

| 40        | 12                         | 33.4                 | 50.0                 | 6.0                  | 21.8         | 42.6                 | 153.8                   |

| 50        | 15                         | 33.6                 | 50.0                 | 6.2                  | 21.7         | 53.0                 | 164.5                   |

| 100       | 30                         | 33.6                 | 50.2                 | 6.1                  | 21.8         | 104.0                | 215.7                   |

Table 6.1: Average switching frequency and conduction losses forone phase of an asymmetric-bridge SR converter.

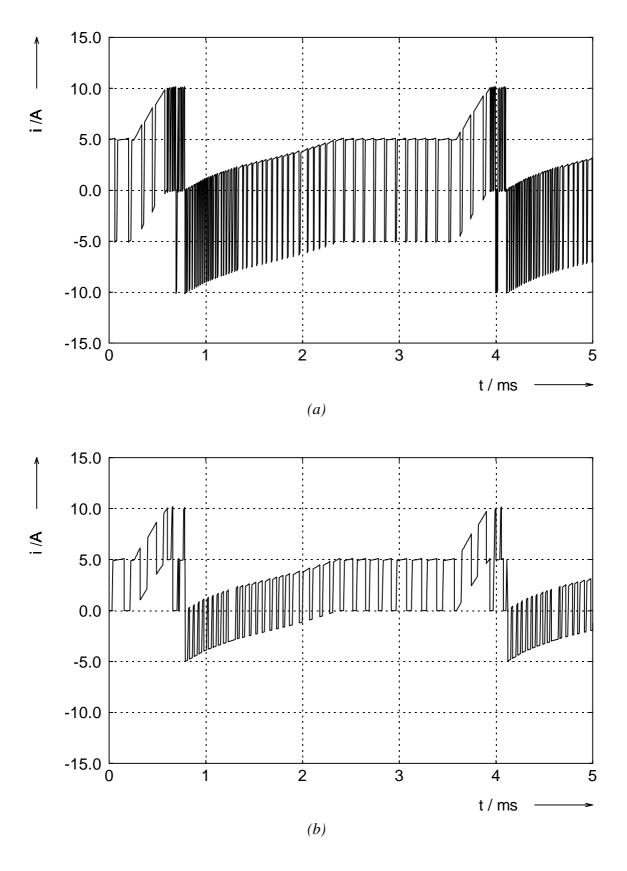

The mean switching frequency shown in column 2 of Table 6.1 has been computed by dividing the number of switchings in a current pulse by the duration of the dwell period. The power values shown in columns 3–6 of Table 6.1 are the conduction losses in the various components of the asymmetric bridge converter, which are identified in Fig. 6.1. Simulation results showing the currents on the branches of the asymmetric bridge for a sampling frequency of 25 kHz are also shown in Fig. 6.1. • the high radial forces acting on the pole tips of stator and rotor can also give rise to mechanical vibrations and cause premature bearing failure at high power levels.

On the other hand, a SRM drive could be an economical replacement for lowpower drive systems using motors which also have inherently high torque pulsations, e.g. single-phase induction motors or universal motors. However, the use of soft-switched SR drives seems to be more attractive in medium power ranges starting at some tens of kW, where the costs of sensors, control circuits, additional components and power electronic devices have a lower weight in the overall costs of the drive system, in comparison with a low-power system. For this reason, the considerations that follow and the simulation results which are presented in this section refer to systems of medium power level.

# 6.2 Optimization of the drive circuit

Depending on the application, it may be more important to enhance other qualities of the ACRDCL SR converter. For instance, if a highly dynamic current control is aimed, one may want to maximize the switching frequency of the main switches in the output stage. A reasonable limit for the switching frequency would be the frequency for which the overall converter losses become equal to the losses of a hard-switching converter of same power rating. In this extreme case, there would be no gain in efficiency, and the cooling should be equally designed for both converters. As a general guideline, it can be assumed that the total switching energy of the power semiconductor devices in an ACRDCL circuit is roughly six times lower than the switching energy of the same devices in a hard-switched converter. This value has been derived from thermal measurements with second-generation IGBT devices [89], operating with a dV/dt value of approximately 400V/µs at turn-off. It is found to hold true within  $\pm 10\%$  for IGBT devices optimized for low conduction losses as well as for devices optimized for faster switching speed. A comparable value of switching loss alleviation is also verified for MCT devices for a turn-off dV/dt of approximately 200V/µs [77].

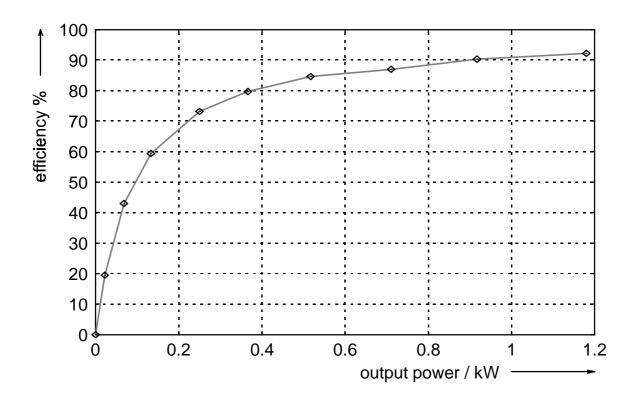

The input and output power of the converter have been measured with a precision high-frequency power meter, for operation in current-regulated mode with a single-phase passive RL load. The efficiency has been then computed and the results are shown in Fig. 5.34.

Fig. 5.34: Converter efficiency with passive load.

The measured total power losses remained approximately constant for the whole output power range considered. This indicates that the power losses in the passive components and on the auxiliary power semiconductor devices in the DC link are dominant with respect to the power loss on the main semiconductor devices in the output section. One reason for this has been the choice of MCTs as main devices. MCTs are commercially available only for current ratings above 65A. At currents under 5A, as was the case in the test circuit, the MCT switching losses are negligible, and it is therefore not possible to measure any reduction of main device switching losses at this current level. A direct comparison between efficiency in the ACRDCL SR converter and in a hard-

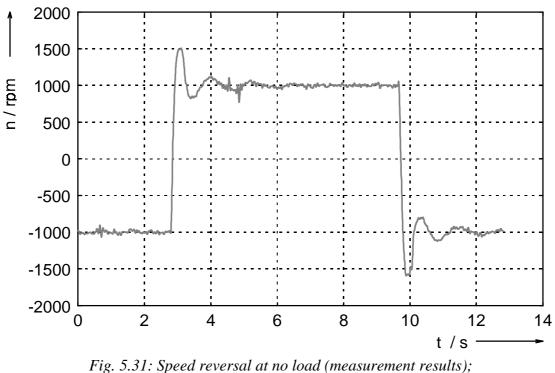

bility, and a limit of 2A has been set for the phase currents, in order to avoid instability of the clamp voltage during braking. As a result, the response is considerably underdamped and somewhat sluggish. The measured speed reversal exhibits a good agreement with the simulation results shown in Fig. 5.25.

total shaft inertia  $J_{SRM} + J_{DC} = 6.4 \times 10^{-4} \text{ kg} \cdot \text{m}^2$ .

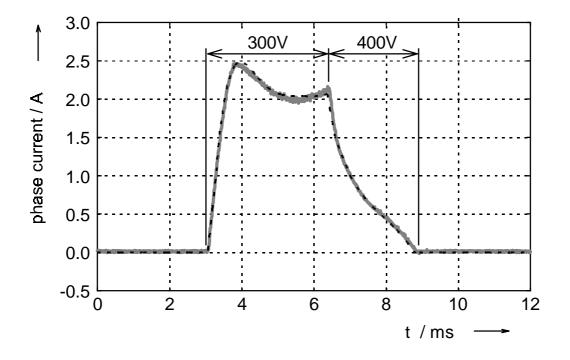

Phase current and voltage waveforms for operation at regenerative braking are shown in figures Fig. 5.32 and Fig. 5.33. During braking operation, the phase current can only be controlled by hard-chopping. The output section injects thereby more energy in the clamp capacitor, which has to be returned to the source through the clamp switch and the resonant inductor. This is achieved by increasing the clamp turn-off current. If the maximum value of the clamp current is limited, there is also an upper limit for the braking current, which can be handled by the clamp circuit without causing instability of the clamp voltage. This limit depends on the size of the clamp capacitor, on the maximum allowable clamp turn-off current and on the dynamic response of the clamp voltage controller.

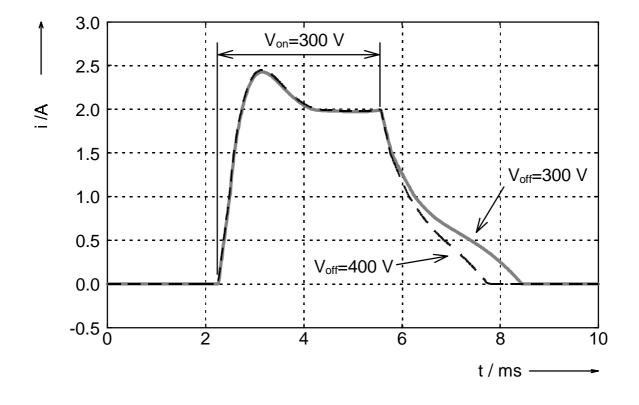

Fig. 5.28: Comparison of measured and simulated (dashed) phase current for single-pulse operation at 1500 rpm.

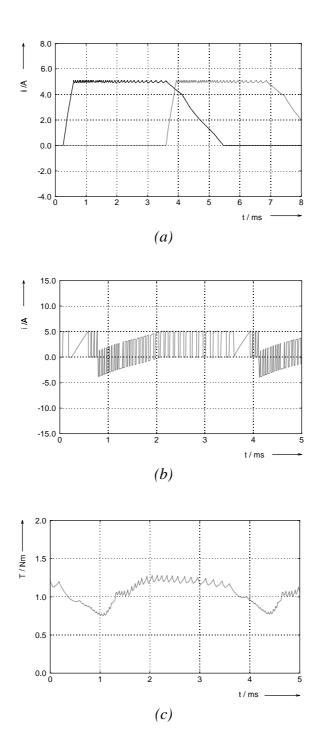

The test circuit has been operated in the current-regulated delta-modulation mode, with a sampling rate of approximately 25 kHz. The phase current and voltage for operation in this mode are shown in figures Fig. 5.29 and Fig. 5.30, for a load torque of approximately 0.5 Nm at 1500 rpm. The resulting mean switching frequency of the main switches in the output section, and the resulting current ripple for this operating mode, depend on the back-emf of the SRM. This, in turn, depend on the phase current level and on the machine speed. For the operating conditions mentioned above, the mean switching frequency lies around 5 kHz.

trol has been implemented using only one current sensor. The sensor is connected to the circuit in such a way, that the phase currents flow through it only during the dwell period or during free-wheeling. However, this phase current control method is somewhat restrictive if the motor is operated with dwell overlap. For this reason, the motor has been operated with a fixed dwell angle of  $30^{\circ}$  (no dwell overlap) and with the optimum turn-off angles determined in section 5.4.3.

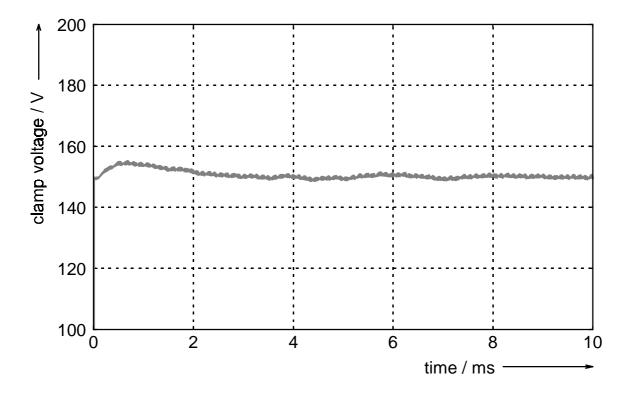

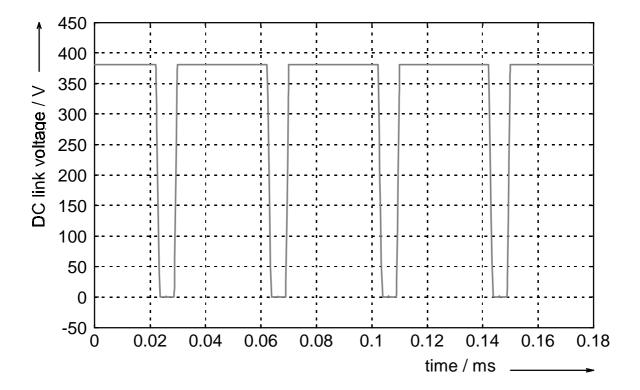

Fig. 5.27 shows the measured voltage at the resonant DC link and the current through the resonant inductor, under no load, for a clamp factor of 1.2. The frequency of the DC link voltage under these operating conditions is approximately 25 kHz, in accordance to the value predicted by equation (5.20). The total no-load losses of the ACRDCL converter have been estimated as approximately 90 W. The validity of the simulation model can be verified by comparing these waveforms to the corresponding simulation results shown in figures Fig. 5.22 and Fig. 5.23. A good agreement between measurement and simulation can also be observed in the current waveforms shown in Fig. 5.28, which have been obtained for single-pulse operation at a speed of 1500 rpm. In both cases, the circuit has been supplied from the rectified single-phase 220V mains.

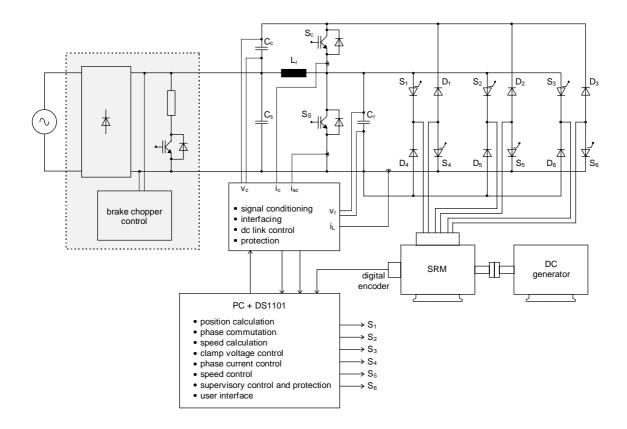

Fig. 5.26: Schematic diagram of the experimental setup.

The output section of the prototype ACRDCL SR converter uses MCTs as main switches. The other auxiliary switches in the circuit are realized with IGBTs. The lower on-state voltage drop of MCTs is very beneficial in an asymmetric-bridge SR converter. Since two switching devices are connected in series to each phase winding, the conduction losses should be as low as possible. With MCTs, the conduction losses can be reduced by as much as 50% with respect to other devices. On the other hand, the inability of the MCT in interrupting short-circuit currents is not critical in an asymmetric bridge SR converter, since the circuit topology itself eliminates the possibility of phase shoot-throughs.

In order to have a minimum of external hardware, most control functions have been implemented in software. Time-critical functions like phase commutation,

*Fig. 5.24: Clamp voltage response to braking current starting at t=0 (simulation results).*

Based on the above results, it can be stated that the braking capability of the ACRDCL SR converter is limited, because the regenerated energy flows through the clamp circuit. Therefore, the braking current must be limited, in order to keep the clamp voltage stable. The dynamic response of the whole drive system has been then simulated, taking into account the braking current limit. A purely inertial load has been used in the simulations, so that the braking capability of the drive system is emphasized, because of the absence of a braking load torque. A proportional + integral (PI) controller has been used for speed control, and its parameters have been set in such a way that the braking current limit is not exceeded. The simulated motor response to a reversion of the speed reference signal from -1000rpm to 1000rpm is shown in Fig. 5.25.

resonant inductor:  $L_r = 60\mu$ H, resonant capacitor:  $C_r = 47$ nF, clamp capacitor:  $C_c = 47\mu$ F.

The circuit has thus the following characteristic quantities:

natural frequency:  $f_r \approx 95 \text{ kHz}$ characteristic impedance:  $Z_r \approx 36 \Omega$

Simulation results showing the voltage across the resonant capacitor, i.e. the resonant DC link voltage, and the current through the resonant inductor under no load are shown in figures Fig. 5.22 and Fig. 5.23.

Fig. 5.22: Resonant DC link voltage (simulation result).

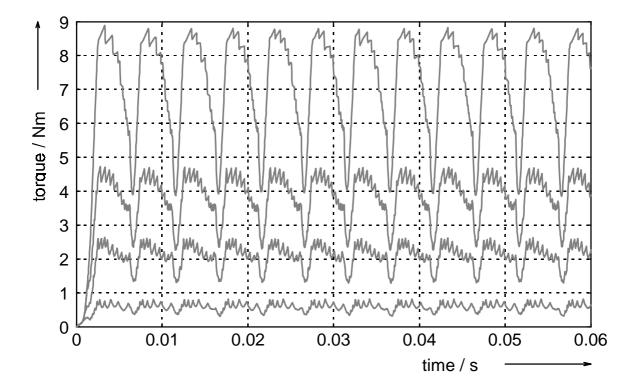

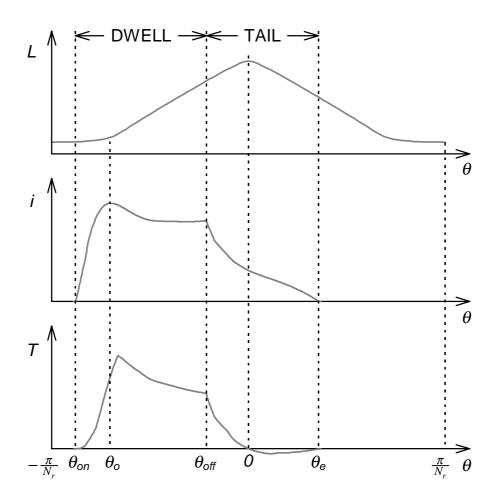

Fig. 5.20 shows running torque waveforms for different current levels, using the optimum commutation angles found above for the speed of 1000 rpm. The relationship between the reference current value and the mean torque for the same conditions as above is shown in Fig. 5.21.

Fig. 5.20: Running torque waveforms at 1000rpm for constant current references of 1A, 2A, 3A and 5A, from bottom to top (simulation results).

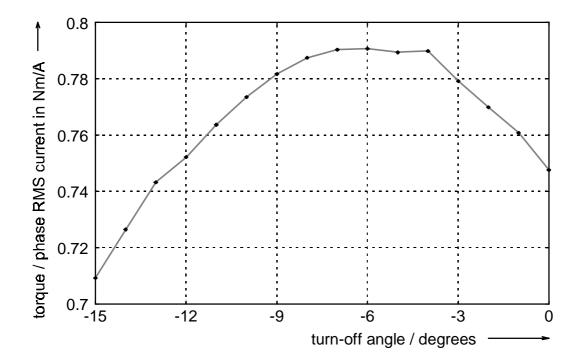

*Fig. 5.16: Torque per phase RMS current versus turn-off angle at 500rpm, for fixed turn-on angle (-45°) and for constant current reference (5A) (simulation results).*

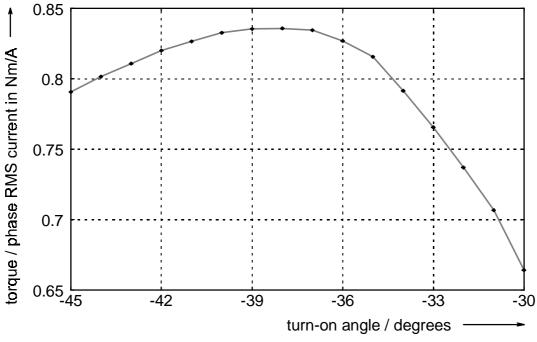

*Fig. 5.17: Torque per phase RMS current versus turn-on angle at 500rpm, for optimum turn-off angle (-6°) and for constant current reference (5A) (simulation results).*

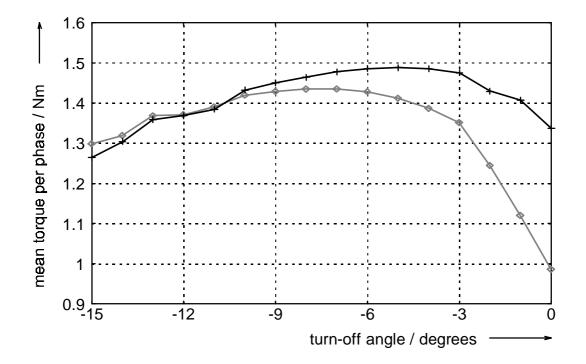

Fig. 5.14: Absolute mean torque produced by one phase versus turn-off angle, for singlepulse operation with fixed turn-on angle (-45°) at 1500 rpm: (o)=conventional SR converter; (+)=ACRDCL SR converter with  $k_c=1.5$  (simulation results).

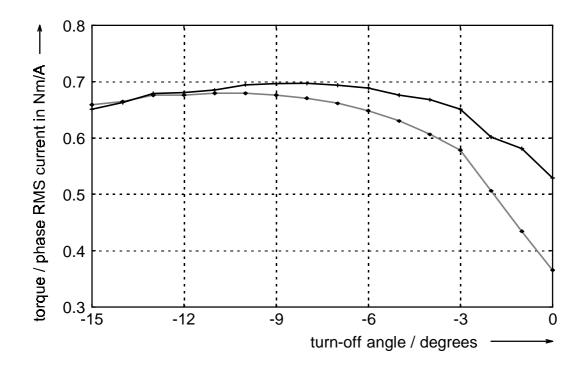

Fig. 5.15: Specific torque (Nm/A<sub>RMS</sub>) produced by one phase versus turn-off angle, for single-pulse operation with fixed turn-on angle (-45°) at 1500 rpm: (o)=conventional SR converter; (+)= ACRDCL SR converter with  $k_c=1.5$  (simulation results).

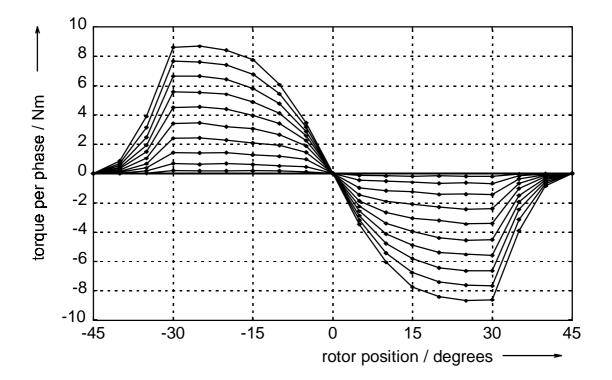

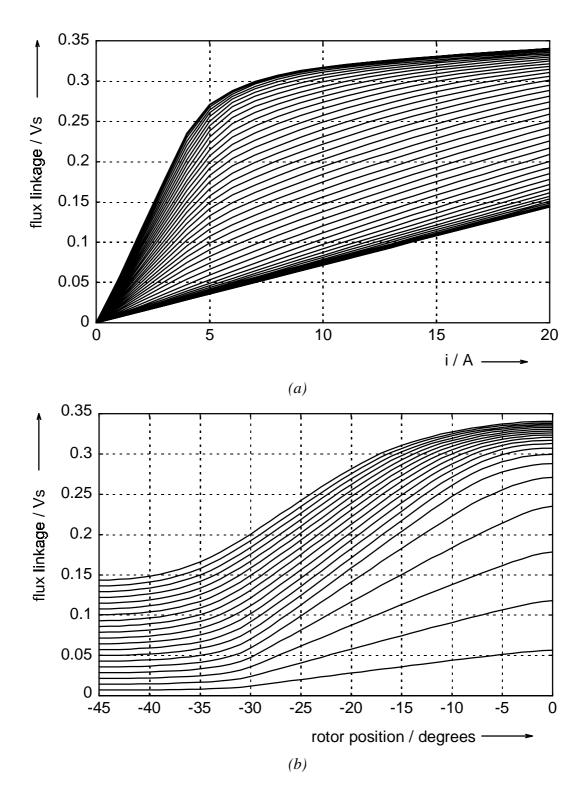

*Fig. 5.12: Measured static torque produced by one phase versus rotor position, for currents varying between 0 and 5A in 0.5A steps.*

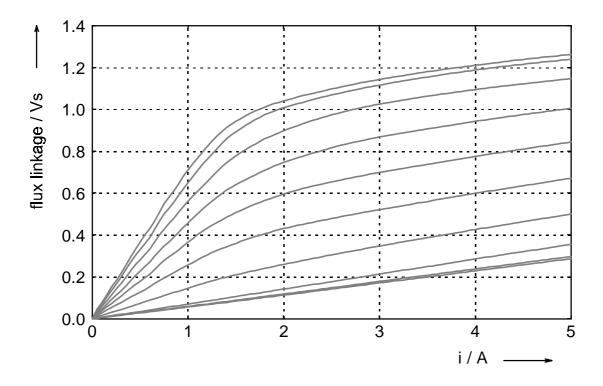

*Fig. 5.13: Measured flux linkage of one phase versus current, for positions varying between -45° and 0° in 5° steps.*

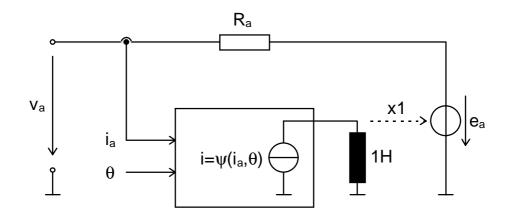

Fig. 5.11: SPICE model for calculation of counter emf for one phase of a SRM.

The structure shown in Fig. 5.11 should be repeated for each phase. Similar subcircuits should also be used to compute the running torque waveforms from the static torque data. The torque contributions from each phase can be then summed up at a common node and integrated by a capacitor connected to the same node. The voltage across this capacitor will be then proportional to the shaft speed.

To keep the computer memory requirements low, the characteristics used in the subcircuits can be tabulated for one electrical half-cycle only. The machine is assumed to be symmetrical, so that the same basic characteristic is used for all phases. The tabulated torque and magnetization data are given in Appendix II. The position information, obtained by capacitive integration of the speed signal, must be remapped to the angle region for which the torque and magnetization characteristics are tabulated, with the due displacements for each phase.

For the power electronic part of the system, simplified quasi-ideal switch models have been used. The use of more accurate models, like that described in [5], for example, demand much longer computing times than an ideal switch model. Therefore, such accurate models are more appropriate for simulation of just a few switching cycles, with the purpose of investigating worst-case device voltage and current stresses. In that case, only the switch itself and a part of the circuit around it need to be modelled in detail. Simulation of lowThe effect of the higher demagnetization voltage provided by the clamp rail over the torque production has been investigated with help from numerical simulations, which are discussed in the following section.

# 5.4 Simulation

The simulation of the ACRDCL SR converter has been executed with the program SPICE, developed at the University of California in Berkeley [102]. The program is public-domain and freely obtainable from the Internet. The current version, that has been used in this work, is version 3f4. SPICE is a circuitoriented analog simulator, i.e. all system components, including controllers, switching control logic and electromechanical subsystems must be described in terms of analog equivalent circuits. These in turn consist on a netlist, containing linear and non-linear analog electric element models. The system is solved using trapezoidal integration with self-adaptive time step. Some commercial implementations of SPICE are also capable of mixed-mode simulation, including digital elements, and behavioral (i.e. transfer-function) models of controllers or other subsystems.

To simulate a complete SR drive system with SPICE, the user should provide a means for representing the highly non-linear magnetization characteristics of the SRM. At each time step, the torque and the counter emf should be computed for each phase, so that the motor equations (2.9) and (2.10) can be solved, as well as the equations for the remaining system. The on-line computation of torque and counter emf should be reasonably accurate and fast, to allow the simulation of lengthy mechanical transients in practical time. A good compromise between accuracy and computational speed is reached if some points of the static torque and magnetization characteristics are tabulated for different positions and current levels, and the actual instantaneous values are then obtained by on-line interpolation [25]. With SPICE, it is not possible to input such a two-dimensional look-up table directly. However, a sub-circuit structure which behaves like a linearly-interpolated look-up table can be de-

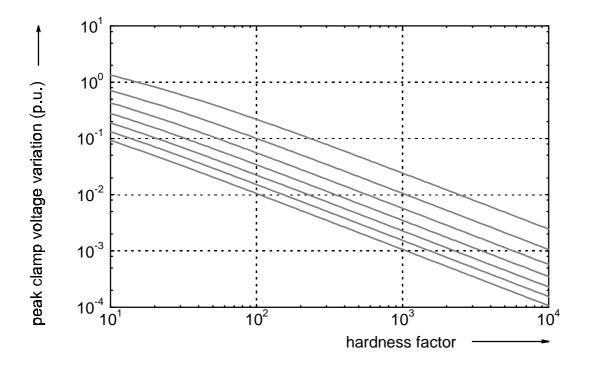

If a "hardness factor" for the clamping process is defined as:

$$k_h \stackrel{\scriptscriptstyle \Delta}{=} \frac{C_c}{C_r},\tag{5.29}$$

then the per unit peak variation of the clamp capacitor voltage can be expressed as:

$$\frac{\Delta v_{C_c \max}}{(k_c - 1) \cdot V_s} = \sqrt{\frac{1 + k_h (k_c - 1)^2 + k_b^2}{(1 + k_h) \cdot (k_c - 1)^2}} - 1.$$

(5.30)

The clamp capacitance can now be selected by establishing an upper limit for the maximum variation of the voltage across the clamp capacitor. The relationship given by (5.30) is represented graphically in Fig. 5.9, as a function of the hardness factor, for a boost factor equal to 1.0 and for different values of clamp factor.

Fig. 5.9: Per unit peak variation of the clamp voltage versus hardness factor for  $k_b = 1$  and  $k_c$  varying from 1.2 (upper trace) to 1.8 (lower trace) in 0.1 steps.

impedance, for a fixed natural frequency, will apparently reduce the overall losses, because the peak DC link current will be lower, causing lower conduction losses in the power semiconductor devices. However, the realization of a higher characteristic impedance at a given natural frequency requires the use of a larger resonant inductance and of a smaller resonant capacitance. Higher values of inductance generally imply larger inductor sizes and higher equivalent series resistance (ESR) values. The total inductor losses can thus be thought of as consisting of two components:

- the loss component associated to the resonant current, which is inversely proportional to the characteristic impedance;

- the loss component associated to the output current, which is directly proportional to the ESR and therefore increases for higher inductance or characteristic impedance values.

Based on the above considerations, it can be stated that there is an optimal value of inductance, and consequently of characteristic impedance, that minimizes the overall converter losses. A rough estimate of the optimum impedance can be obtained by modeling the DC link current as a high-frequency sinusoidal at the resonant frequency (amplitude  $V_s/Z_r$ ) superimposed to a rectified sinusoidal at the DC link fundamental frequency (amplitude  $I_o$ ). In this case, the overall inductor losses can be easily written as:

$$P_{L} = \frac{1}{2} ESR \cdot \left( I_{o}^{2} + \frac{V_{s}^{2}}{Z_{r}^{2}} \right).$$

(5.24)

If the ESR of the resonant inductor is written as the product  $Q \cdot L_r$ , where Q is the quality factor of  $L_r$ , then the minimum of (5.24) can be found to occur for:

$$Z_r = \frac{V_s}{I_o} \quad . \tag{5.25}$$

It has been verified empirically by some authors [75, 89] that the above relationship yields a good compromise between inductor size, overall power losses

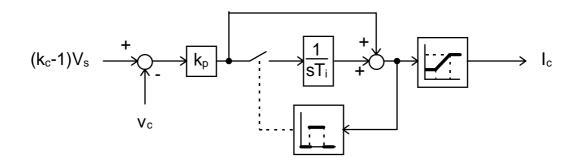

Fig. 5.8: Clamp voltage control.

If the clamp capacitance is large, so that the clamp voltage changes much slower than the DC link oscillation, then the current that flows into the clamp capacitor can be averaged, and its variation can be considered equal to the variation of the actuating signal  $I_c$ . In this case, the response of the clamp voltage to small variations of the clamp voltage reference is approximately governed by the following transfer function (Appendix III):

$$G(s) = \frac{1 + sT_i}{1 + sT_i + s^2 \frac{T_i C_c}{k_p}}.$$

(5.21)

The response of the clamp voltage control to sudden variations of the net current injected in the clamp capacitor, as occurs for instance when the motor is braked, is approximately given by (Appendix III):

$$\frac{\Delta V_c(s)}{\Delta I_c(s)} = \frac{sT_i/k_p}{1+sT_i+s^2\frac{T_iC_c}{k_p}}.$$

(5.22)

### 5.2 Design criteria

For the successful design of an ACRDCL converter, it is important to choose appropriate values for the natural frequency and for the characteristic imped-

$$I_{o} = \sqrt{I_{c}^{2} - k_{c} \left(2 - k_{c}\right) \left(\frac{V_{s}}{Z_{r}}\right)^{2}},$$

(5.17)

and this is the initial current for the boost period of the next cycle.

The period of the resonant DC link pulsation is given by the sum of the intervals (5.4), (5.8), (5.13) and (5.17):

$$T = T_{boost} + T_{rise} + T_{clamp} + T_{fall}.$$

(5.18)

If a "boost factor"  $k_b$  is defined as:

$$k_b = \frac{I_T}{\left(V_s/Z_r\right)},\tag{5.19}$$

then, the DC link frequency can be found to be given by:

$$f = \frac{\omega_r}{2\left[k_b + \frac{\sqrt{k_b^2 + k_c \cdot (2 - k_c)}}{(k_c - 1)} + \sin^{-l}\left(\frac{(k_c - 1)}{\sqrt{1 + k_b^2}}\right) - \tan^{-l}\left(-\frac{1}{k_b}\right)\right]}.$$

(5.20)

A plot of the ratio between the DC link no-load frequency and the natural frequency of the resonant tank, as a function of the clamp factor and for different values of boost factor is shown in Fig. 5.7. In a typical application, the clamp factor would be, for instance,  $k_c$ =1.5 and the boost factor,  $k_b$ =1.0, yielding a DC link frequency equal to approximately 65% of the natural frequency  $f_r$  of the resonant tank. So, for typical  $f_r$  values of approximately 80 kHz, the DC link frequency would lie around 50 kHz.

$$v_{C_{c}}(t) = \sqrt{\left(k_{c} - I\right)^{2} V_{s}^{2} + Z_{r}^{\prime 2} I_{co}^{2}} \sin\left[\omega_{r}^{\prime}\left(t - t_{d}\right) + \tan^{-l}\left(\frac{\left(k_{c} - I\right) V_{s}}{Z_{r}^{\prime} I_{co}}\right)\right]; \quad (5.9)$$

$$i_{c}(t) = \sqrt{I_{co}^{2} + \frac{(k_{c} - I)V_{s}^{2}}{Z_{r}^{\prime 2}}} \sin\left[\omega_{r}^{\prime}(t - t_{d}) + \tan^{-I}\left(-\frac{Z_{r}^{\prime}I_{co}}{(k_{c} - I)V_{s}}\right)\right]; \quad (5.10)$$

where:

$$\omega_r' = \frac{1}{\sqrt{L_r(C_r + C_c)}}; \qquad (5.11)$$

$$Z_r' = \sqrt{\frac{L_r}{\left(C_r + C_c\right)}}.$$

(5.12)

In the steady state, the final value  $I_c$  of the clamp current should be equal to the initial value  $I_{co}$ , so that the net charge transferred to the clamp capacitor is zero, keeping the clamp voltage regulated. If the clamp capacitor is large, the duration of the clamp period is approximately given by:

$$T_{clamp} \cong 2 \cdot \frac{|I_{co}| \cdot L_r}{(k_c - 1) \cdot V_s}.$$

(5.13)

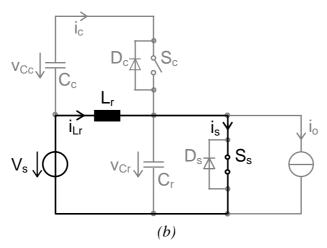

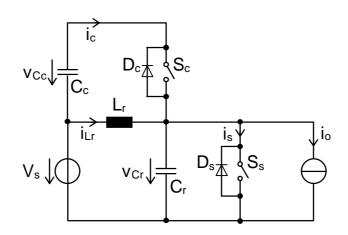

#### falling resonant transition (from f to a)

The active path during the falling resonant transition is shown in Fig. 5.6. As in the case of the rising resonant transition, only the elements of the resonant tank are active. At  $t = t_f$ , switch  $S_c$  is turned off and the link current begins to be drained from the resonant capacitor  $C_r$ . The initial current in  $C_r$  will be the "trip" current value  $I_c$ , which was flowing through  $S_c$  at the end of the clamp period. The voltage  $v_{Cr}$  will then immediately start a falling oscillation, and this period ends when  $v_{Cr}$  reaches the zero voltage level, when  $D_s$  begins to conduct (instant a), starting a new cycle.

The link voltage and current during this period can be written as:

$$v_{C_r}(t) = V_s + \sqrt{V_s^2 + Z_r^2 I_T^2} \sin \left[ \omega_r (t - t_c) + tan^{-l} \left( -\frac{V_s}{Z_r I_T} \right) \right];$$

(5.5)

$$i_{L_r}(t) = \sqrt{I_T^2 + \frac{V_s^2}{Z_r^2}} \sin \left[ \omega_r (t - t_c) + tan^{-l} \left( \frac{Z_r I_T}{V_s} \right) \right].$$

(5.6)

The duration of the rising resonant transition is given by:

$$T_{rise} = \frac{1}{\omega_r} \left[ sin^{-l} \left( \frac{(k_c - l)}{\sqrt{1 + \frac{Z_r^2 I_T^2}{V_s^2}}} \right) - tan^{-l} \left( -\frac{V_s}{Z_r I_T} \right) \right].$$

(5.7)

#### **clamp period** (from d to f)

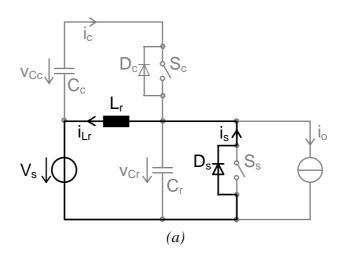

The equivalent circuits for the clamp period are shown in Fig. 5.5. The diode  $D_c$  begins to conduct (instant d) when the DC link voltage reaches the clamping level  $k_c \cdot V_s$ . While  $D_c$  is conducting (Fig. 5.5 (a)), the clamp switch  $S_c$  can be turned on under ZVS conditions. If the clamp capacitor is large enough, the link voltage  $v_{Cr}$  and the clamp voltage  $v_{Cc}$  remain approximately constant during the whole clamping process. In this case, the current  $i_{Lr}$  decreases almost linearly, until the clamp current  $i_c$  reverses and begins to flow through the switch  $S_c$  (instant e, Fig. 5.5 (a)).  $S_c$  is kept closed until  $i_c$  reaches a preset value  $I_c$ , at which  $S_c$  is turned off, ending the clamp period.  $S_c$  is also switched off under ZVS conditions, because  $C_c$  and  $C_r$  do not allow a sudden change of the voltage at its terminals.

conducts the link current from the preceding cycle, which flows back to the DC supply. The magnitude of  $i_{Lr}$  decreases linearly thereby, under the influence of the supply voltage  $V_s$ . While  $D_s$  is conducting, switch  $S_s$  can be turned on under nearly zero voltage, with low turn-on losses. Eventually,  $i_s$  reverses and begins to flow through  $S_s$  (instant **b**, Fig. 5.3 (b)).  $S_s$  is then kept closed for a short period of time, during which  $i_{Lr}$  is further linearly boosted. At a preset time after turn-on of  $S_s$ , or when  $i_s$  reaches a preset "trip" current level  $I_T$ , switch  $S_s$  is turned off (instant **c**), ending the boost period.  $S_s$  is switched off at ZVS conditions, because  $C_r$  does not allow a sudden change of the voltage across it.

Fig. 5.3: Active paths during the boost period (a) between instants **a** and **b** (b) between instants **b** and **c**

Fig. 5.1: Equivalent circuit for the ACRDCL.

The waveforms of the DC link voltage  $v_{Cr}$  and of the DC link current  $i_{Lr}$ , in steady-state under no load ( $i_o = 0$ ), are shown in Fig. 5.2. One cycle of the DC link operation comprises a sequence of states, whose changes are characterized by the instants described in Table 5.1, also labelled in Fig. 5.2:

Table 5.1: Operating sequence of the ACRDCL.

| instant | state changes                   |

|---------|---------------------------------|

| a       | $D_s$ conducts                  |

| b       | $D_s$ turns off, $S_s$ conducts |

| С       | $S_s$ turns off                 |

| d       | $D_c$ conducts                  |

| e       | $D_c$ turns off, $S_c$ conducts |

| f       | $S_c$ turns off                 |

film capacitors. Another potential advantage of MLC technology is its suitability for integration, in the sense that is discussed in [88].

To illustrate the potential size reduction achievable by using the appropriate capacitor technology, a comparison between ceramic and electrolytic technologies is now presented. The data are taken from the clamp capacitor design for the ACRDCL SR converter, which is analyzed with more detail in chapter 5. Preliminary calculations show that the capacitor should have a capacitance value of 47µF at a working DC voltage of 150V. The RMS current ripple capability must be higher than 8.1A at 25kHz. If a single aluminum electrolytic capacitor is used, the smallest capacitor that matches the current ripple requirement has a capacitance of 2200µF (approximately 47 times higher than the required value) at a voltage rating of 200V, a volume of 20cm<sup>3</sup> and weights approximately 100g. The ESR is approximately  $33m\Omega$ , yielding a power loss of ca. 2W. Additionally, it is very likely that one or more film capacitors with low equivalent series inductance (ESL) will have to be connected in parallel to the electrolytic capacitor, in order to provide a path for the high-frequency current components and to avoid voltage spikes provoked by the high di/dt on the ESL of the electrolytic capacitor. On the other hand, if a ceramic capacitor is used, the current ripple requirement can be matched by a capacitor of exactly  $47\mu$ F, 200V, having only half the volume of the electrolytic capacitor, with an ESR of  $7m\Omega$  and power losses lower than 0.5W.

losses at higher frequencies. Large air gaps are also recommended, in order to keep the induction and consequently the magnetic losses low. Some studies [9, 75] have shown that the use of low-permeability materials to provide a "distributed air gap" can lead to better performance. A pot core with a shortened center post can also be a good compromise between volume, weight, losses and EMI. In this case, the inductor is essentially an air core inductor, but there is a magnetic shield around it.

Another inductor design concept that is gaining increasing acceptance is the planar design. Planar inductors with sheet-conductor or printed-circuit windings can be very compact, attaining higher power densities. At higher power levels, the planar design can be even more advantageous, because it also provides an improved thermal interface due to the large surfaces available for cooling.

# 4.2.2 Capacitors

In ACRDCL converters, basically three "types" of capacitors are needed, depending on the location in the circuit where they are used:

- the resonant capacitor;

- the clamp capacitor;

- the DC supply capacitor.

For each of the above types, there are different design requirements, according to the required capacitance range and to the nature of the current that flows through the capacitor. Therefore, a different capacitor technology may be the most appropriate for each location in the circuit. Capacitors are available today in three basic technologies, for use in power electronic circuits up to some hundreds of kilowatts. Currently commercially available technologies are listed below [91]:

#### 4.2.1 Inductors

Air core inductors can be a good choice for some applications, because they produce no core losses and can be lighter than inductors with a magnetic core, but volume and radiated EMI are limiting factors. In addition, at higher power levels, air core inductors can be constructed with smaller dimensions than magnetic core inductors, because the magnetic core may have to be overdimensioned due to thermal problems [75]. EMI radiation can be reduced if a toroidal winding is used, where most of the magnetic flux remains confined in the interior of the winding. The inductance of a toroidal coil with air core can be estimated by

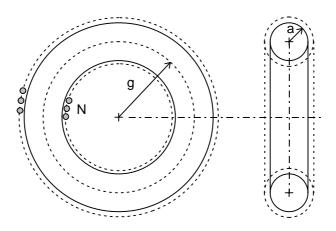

$$L = \mu_0 N^2 \left( g - \sqrt{g^2 - a^2} \right), \tag{4.2}$$

where N is the number of turns, g is the mean radius of the torus and a is the radius of its cross section, as shown in Fig. 4.4.

Fig. 4.4: Top view and cross section of toroidal coil.

The winding construction is also very critical with respect to the power losses and the size of resonant inductors designed for operation under high peak values of alternating current and at higher frequencies, because of skin and prox-

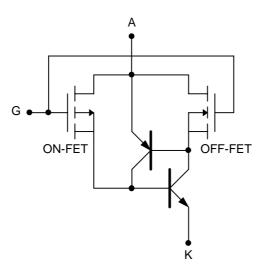

Fig. 4.3: Equivalent circuit of the p-MCT.

The major advantage of MCTs in comparison with IGBTs is the up to 50% lower on-state voltage, which can lead to an up to 50% reduction of the onstate power losses [76]. Typical values of on-state voltages are between 1V and 1.5V for MCTs rated at 1kV, whereas 3rd generation IGBTs of comparable voltage rating exhibit saturation voltages about 2V to 2.5V. On the other hand, MCTs exhibit somewhat higher switching losses than IGBTs in hard-switched mode. Typical values of total switching losses (specific values, normalized to rated current) are under 0.3 mJ/A [77, 98]. Furthermore, the MCT tail current is strongly dependent on the temperature, leading to higher turn-off losses at higher temperatures. Tail current duration is typically about 1µs.

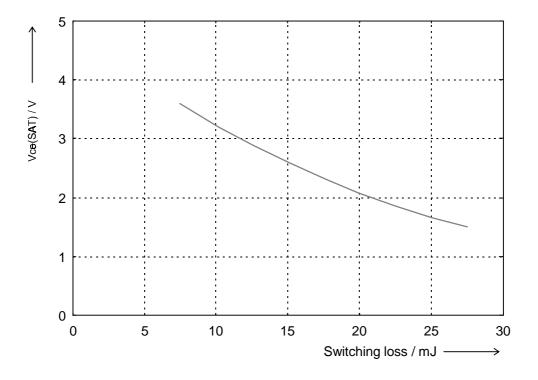

The main drawback of the MCT is its restricted capability to limit and to turn off short-circuit currents. MCTs can conduct much higher currents than IGBTs with the same chip size. However, MCTs and IGBTs have approximately the same maximum turn-off current density, so that there is no chip size advantage if both components are designed to have the same short-circuit ratings. In fact, the MCT turn-off capability depends on the on-state resistance of the off-FET region. When the device is being turned off, the full cathode current flows through the off-FET. If the voltage drop across it is greater than the baseemitter voltage of the npn transistor in the thyristor pair, this latter cannot be achievable on-state voltage versus total switching energy for a secondgeneration 600V IGBT is shown in Fig. 4.2.

Fig. 4.2: Typical  $V_{CE}(on)$  versus switching energy relationship for a 600V IGBT at  $1A/mm^2$ .

Most manufacturers have developed basically two types of second-generation IGBT devices, one optimized for lower on-state voltage drop and consequently lower conduction losses, and another optimized for faster switching speed and lower switching losses. These families have been usually called "low saturation" and "fast switching" respectively. However, further optimization of IGBT chip properties has led to third-generation devices, which exhibit equal or lower conduction losses than second-generation low saturation devices and equal or lower switching losses than second-generation fast switching devices. Typical values of specific switching losses of second- and third-generation devices are shown in Table 4.1 [5, 36, 64].

Another important property related to the unipolar structure of the MOSFET is the very high switching speed. As there is no injection of minority carriers in the drift layer during conduction, there is neither delay nor tail current associated with removal of excess carriers at turn-off. The turn-on process is also very fast, mainly governed by the movement of charge carriers in the depletion layer and in the gate-source stray capacitances. Consequently, switching frequencies up to some hundred kHz can be easily reached in hard-switching mode. If soft-switching is used, the switching frequency can be increased up to some MHz [48]. However, due to the trade-off between current and voltage ratings mentioned above, the use of MOSFETs in electric motor drives is limited to low-voltage and low-power ranges.

### 4.1.2 IGBT

There are basically two types of IGBT, termed punch-through (PT) and nonpunch-through (NPT). The main difference between the two types is the presence of a highly doped n+ buffer layer in the PT IGBT vertical structure, as shown in Fig. 4.1 (b). The purpose of this buffer region is to limit the extent of the depletion layer for blocking voltages higher than a fraction of the device's breakdown voltage. This allows for reduction of the drift region thickness, with attendant reduction of conduction losses. This buffer layer is not present in the NPT IGBT structure, which must therefore have a wider drift region to achieve the same voltage rating. Since this drift region is only lightly doped (low conductivity), conduction losses are expected to be higher than for the PT geometry.

The switching behaviour of the IGBT is also influenced by the type of structure [67,82]. Although the switching mechanisms are basically the same in both structure types, differences in emitter efficiencies and in carrier lifetimes give rise to different magnitudes and durations of the so-called tail current at turn-off. The emitter efficiency influences directly the portioning of the total device current in the two components  $i_1$  and  $i_2$  shown in Fig. 4.1 (b). Component  $i_1$  is a BJT-like current, and its path can be viewed as a pnp bipolar transistor. This

**MOSFET** (Metal-Oxide-Semiconductor Field Effect Transistor) - for low to medium power applications up to some kW. However, high blocking voltage and high current conduction capabilities cannot be attained simultaneously. Low-current devices with voltage ratings up to 1 kV or low-voltage devices with current ratings up to some hundred amperes are commercially available.

**IGBT** (Insulated Gate Bipolar Transistor) - for medium power applications (<1 MW). By the time of writing of this work, IGBT modules with voltage blocking capabilities up to 3300V and current ratings up to ca. 1 kA have become commercially available [72].

**MCT** (MOS-Controlled Thyristor) - an emerging device. Current and voltage ratings of MCTs comparable to those of IGBTs are technically possible, but currently available devices have voltage ratings up to 1 kV and current ratings less than 100 A.

As high power applications are beyond the scope of this work, SCRs and GTOs are not dealt with in the following analysis. BJTs are also not considered because of its on-going obsolescence.

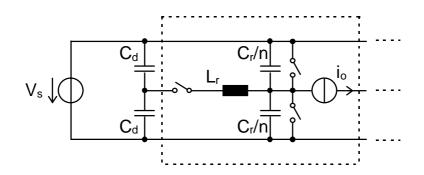

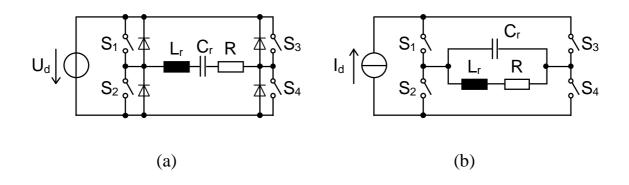

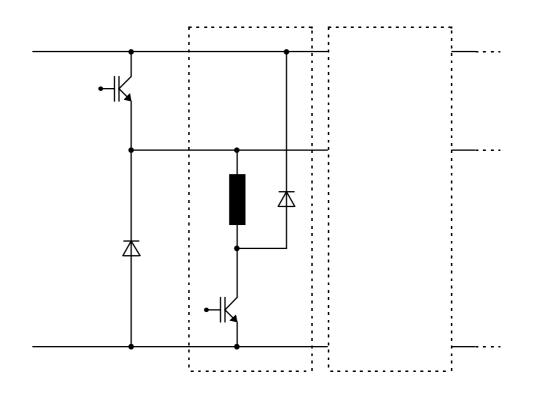

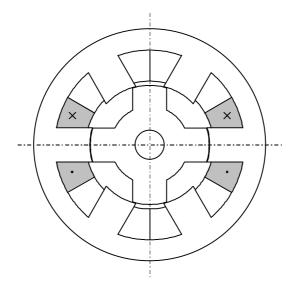

MOSFETs, IGBTs and MCTs have high-impedance (isolated) control terminals and consequently lower power consumption at the gate terminal, in comparison to SCRs, GTOs and BJTs. A simplified comparison of the vertical structures of these devices is presented in Fig. 4.1. Their basic features are discussed below [67]. Although the actively-clamped resonant DC link (ACRDCL) converter has been frequently pointed out as the most promising resonant converter topology for medium-power AC drive systems, no other author has published any work on attempting to adapt an ACRDCL converter for application in SR drive systems. Nevertheless, the ACRDCL seems to be a well-suited soft-switching circuit for high power density SR drives, because it has a low number of additional components and the voltage stresses are limited, according to the clamp factor. A possible implementation of ACRDCL SR converter is shown in Fig. 3.16. A detailed analysis of the ACRDCL SR converter is presented in chapter 5.

Fig. 3.16: A possible implementation of ACRDCL SR converter.

used only to resonate the DC link voltage to zero, in order to create a zerovoltage switching opportunity for commutation of the main output switches. As switch S must conduct the whole motor current, the conduction losses are expected to be up to ca. 30% higher, for operation in single-pulse mode.

#### **3.2.4 AQRDCL SR converter**

In [15], the application of an auxiliary quasi-resonant DC link (AQRDCL) to a SR machine drive is proposed. A schematic diagram of the proposed circuit is shown in Fig. 3.15. In this topology, the switch  $S_c$  is kept closed most of the time, connecting the supply voltage  $V_s$  to the upper rail of the output section. When the main output switches have to be commutated, a resonant transition is started by triggering the auxiliary zero-current switch  $S_a$  into conduction, in order to pre-charge the resonant inductor  $L_r$ . Switch  $S_a$  is kept closed until the energy is stored in  $L_r$  is enough to ensure a full swing of the DC link voltage from  $V_s$  to zero. Switch  $S_c$  is then turned off under ZVS conditions, and the DC link voltage falls to zero with the waveshape dictated by the resonant tank formed by  $L_r$  and  $C_r$ . When the DC link voltage passes through zero, the switch  $S_s$  is closed, shorting the DC bus and holding its voltage at zero for a brief period, during which the main output switches can be commutated with low switching losses. The duration of this shorting period should be enough for the current in  $L_r$  to reverse and to reach a magnitude that will guarantee the full swing of the DC link voltage back to  $V_s$  when the switch  $S_s$  is turned off.  $S_s$  is switched off under ZVS conditions, and the energy stored in  $L_r$  will give rise to the resonant oscillation with  $C_r$ , that will bring the DC link voltage back to the supply level  $V_s$ .

In the circuit of Fig. 3.15, switch  $S_a$  must be bi-directional in voltage and current. Furthermore, switch  $S_c$  conducts the whole motor current, producing additional conduction losses. If the circuit is operated with tail current overlap, the voltage applied to an offgoing phase during demagnetization will be reduced, because of the DC link resonance required for PWM current control of the next ongoing phase. This shortcoming can be avoided if the upper diodes of between  $-V_s$  and  $+V_s$  in order to control the phase current. This requires an interleaving or time-multiplexing of both control loops, and it may be difficult to achieve when the switching frequencies in the two phases are different, due to different current levels. As a result, the turn-off of a phase is strongly coupled to the turn-on of the next phase. In this circuit, the peak voltage stresses can be limited by choosing an appropriate value for  $\Delta V$ . The peak current stresses are also directly proportional to  $\Delta V$  and inversely proportional to the characteristic impedance of the resonant tank  $Z_r = \sqrt{L_r/C_r}$ . The reduced number of switches seems to be the main advantage of this circuit, but they must be rated to more than twice the supply voltage, so the cost savings are low. Furthermore, the control method employed for this converter is very complex and it is expected to exhibit a slower dynamic performance than a directly voltage-fed CRPWM control.

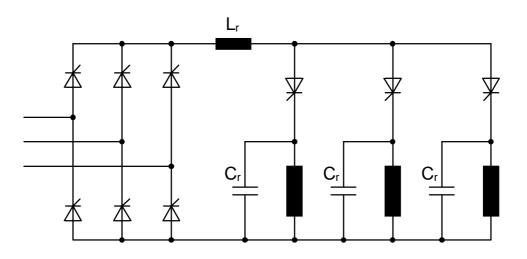

Fig. 3.13: Series-resonant converter for 6/4 SR motor, with three-phase input.

### 3.2.3 Zero-voltage transition (ZVT) PWM SR converter

In [71], Rim et al. propose the use of a single chopping switch to regulate the DC link voltage of a "Pollock" converter, using true PWM voltage control. The chopping switch (*S*) is commutated at zero voltage with help from a subcircuit comprising a resonant tank ( $L_r$  and  $C_r$ ) and an auxiliary switch ( $S_a$ ), as shown

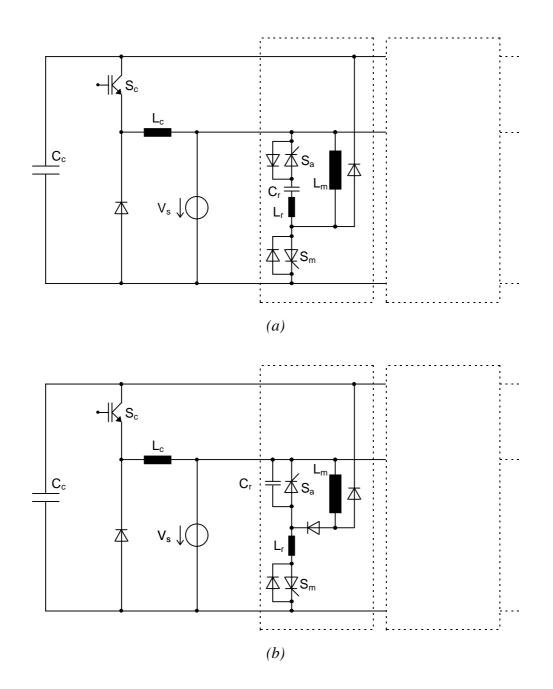

diodes makes the turn-on behaviour of the main switches to be dictated by the reverse recovery characteristics of the C-dump diodes, resulting in no alleviation of turn-on losses. In fact, both circuits are more likely to be classified as force-commutated thyristor converters than as actual soft-switching topologies. The high number of components is the major disadvantage of these circuits.

the output stage can be commutated under zero voltage, with low switching losses. The moments when the DC link oscillation is triggered to create a zero-voltage soft-switching opportunity can be almost freely chosen, provided the resonant frequency is substantially higher than the average switching frequency of the output converter.

The higher degree of freedom in choosing the commutation instants, compared to resonant link converters, enables the utilization of quasi-PWM methods for the output voltage or current control, rendering improved spectral characteristics. However, if simultaneous control of several output phases is required, they cannot be controlled completely independently from each other, because there is only one resonant commutation circuit for all phases. If the output section is composed by half-bridge inverter phase legs, the switch  $S_s$  can be removed from the circuit and its function can be performed by the phase legs.

The topologic similarity between the ACRDCL and the AQRDCL should be noticed. If switch  $S_a$  is suppressed or kept closed all the time, the AQRDCL can be operated as an ACRDCL in buck mode, with continuously resonating DC link voltage. In this case, the average DC link voltage will be lower than the supply voltage. On the other hand, the ACRDCL circuit shown in Fig. 3.6 is a boost implementation, that allows full utilization of the supply voltage at the output. In the boost ACRDCL, the main power flow occurs through the resonant inductor, which therefore has to be designed for very low power losses. Conversely, in the buck ACRDCL and in the AQRDCL, the main power flow takes place at switch  $S_c$ .

## 3.2 Soft-switching converters for SR drives

The use of soft-switching converters in AC machine drive systems has been already well documented in the literature, with many works having been published, e.g. [8, 19, 21, 22, 39, 44, 45, 73, 89, 96, 97]. On the other hand, just a few reported applications of soft-switching techniques in SR drive systems are

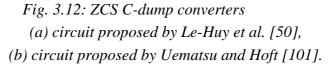

## 3.1.3.3 Resonant pole converters

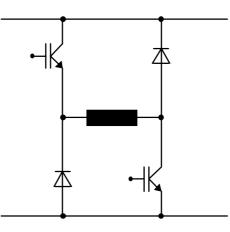

The family of resonant pole converters is characterized by the presence of a so-called resonant pole at each leg of the output section. Each resonant pole comprises a resonant inductor and a pair of resonant capacitors. These capacitors are directly connected in parallel with the main output switches, in order to achieve zero-voltage switching. Some resonant pole topologies, like the auxiliary resonant commutated pole (ARCP) converter [13], also include additional switching devices in order to improve the controllability and reduce the current stresses and the conduction losses in the resonant pole. An equivalent circuit for one phase of the ARCP converter is shown in Fig. 3.10. The circuit section enclosed in the dashed box is equal for each output phase. The middle point provided by capacitors  $C_d$  is common to all phases.

Fig. 3.10: Equivalent circuit for one phase of the ACRP converter.

In contrast to resonant DC link converters, no resonance is produced at the DC link in resonant pole converters. Instead of that, the resonant transitions occur separately at each resonant pole, only when the switches in the output stage need to be commutated. The DC link voltage remains unaffected during the resonant transitions. Therefore, the main switches in the inverter phase legs can be commutated totally independent from each other. This allows a free choice of the commutation instants, thus enabling the employment of "true" PWM control techniques.

104] that the ACRDCL is the most suitable soft-switching converter topology for medium-power AC drive applications.

## Series resonant DC link (SRDCL) converter

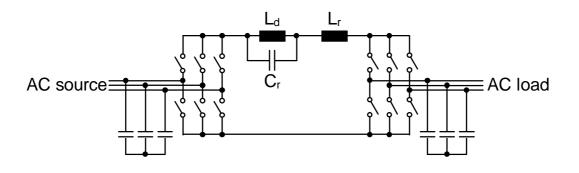

The SRDCL converter [68] is obtained by adding a resonant tank to a currentregulated DC link converter. An example of three-phase AC to three-phase AC SRDCL converter is shown in Fig. 3.8. The topology is very similar to the SRACL converter, but in this circuit, the switches do not need to conduct in both directions as in the SRACL. However, they must be capable of blocking direct and reverse voltage. The DC link current of the SRDCL converter can be described as the sum of a high-frequency AC component (as in the SRACL), produced by the resonant tank, plus a DC bias provided by the smoothing inductor  $L_d$ . To provide this DC offset,  $L_d$  must be much larger than the resonant inductor  $L_r$  and its current must be regulated by controlling the output voltage of the source-side converter. The input and output switches are commutated with low switching losses, when the resonant DC link current crosses zero, hence under ZCS conditions.

Fig. 3.8: SRDCL converter.

The operation of the SRDCL converter is in many aspects dual to the operation of the PRDCL converter. The duality can be better understood with help of the equivalent circuit shown in Fig. 3.9. The current source  $I_d$  is used to represent the current in the smoothing reactance  $L_d$  (Fig. 3.8), because the current in  $L_d$  does not change appreciably during one resonant cycle. Comparing this circuit

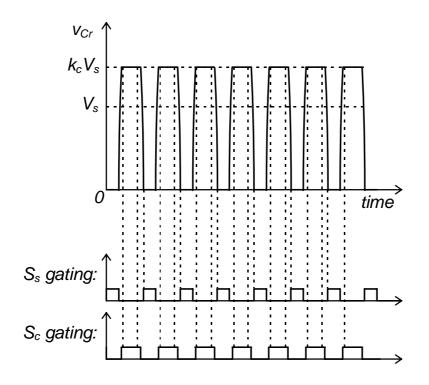

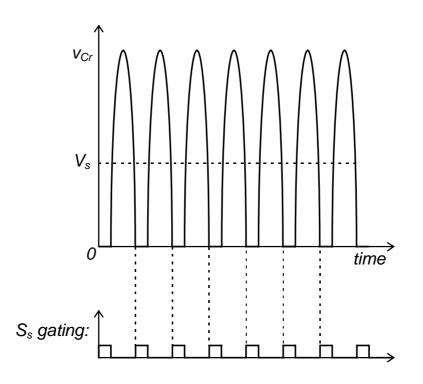

The modeling assumptions mentioned above for the PRDCL converter are also valid for the ACRDCL converter. Circuit operation of the ACRDCL is also very similar to that of the PRDCL. An operating cycle starts when switch  $S_s$  is switched on.  $S_s$  is kept closed until enough energy is stored in  $L_r$  to ensure that a full resonant cycle will be completed.  $S_s$  is then released, the current through  $L_r$  is pumped into the resonant capacitor  $C_r$ , and the voltage  $v_{Cr}$  across  $C_r$  starts to rise towards its natural peak. When  $v_{Cr}$  reaches a value equal to  $(V_s + v_{Cc})$ , the clamping process starts. The clamp diode across  $S_c$  begins to conduct, diverting the current from the resonant capacitor into the clamp capacitor. While the clamp diode is conducting, switch  $S_c$  can be turned on, under zero voltage conditions and with low switching losses.  $S_c$  is kept on until the current in the clamp capacitor reverses and reaches a preset current level  $I_c$ , at which  $S_c$  is turned off. Immediately after turn-off of  $S_c$ , the inverted current which was flowing in the clamping circuit will be transferred back to  $C_r$ , causing the DC link voltage to oscillate toward zero. When  $v_{Cr}$  reaches zero, the anti-parallel diode of  $S_s$  will conduct and then a new cycle can be initiated. The resulting DC link voltage waveform is qualitatively shown in Fig. 3.7.

Fig. 3.7: DC link voltage of the ACRDCL converter.

resonant DC link and ensure that the subsequent oscillation will bring the DC link voltage back to zero. Switch  $S_s$  can now be released and, after the DC link voltage has performed a complete oscillation and returned to zero,  $S_s$  is turned on again in order to give continuity to the process. The resulting DC link voltage waveform is qualitatively shown in Fig. 3.5. While  $S_s$  is closed, the main output switches can be commutated under zero-voltage switching conditions, distributing the DC link voltage pulses among the output phases. When  $S_s$  is opened, the presence of the resonant capacitor  $C_r$  in parallel to it ensures that its own turn-off also occurs under zero-voltage switching conditions. The excess energy stored in  $L_r$  while  $S_s$  is closed will generate a peak DC link voltage higher than twice the supply voltage. When the DC link voltage oscillates downwards, it will tend to become negative, but will be clamped at zero volts by the anti-parallel diode of  $S_s$ . While the diode is conducting,  $S_s$  can be turned on without switching losses, also under zero-voltage switching conditions.

Fig. 3.5: DC link voltage of the PRDCL converter.

## 3.1.3.1 Resonant AC link converters

In resonant AC link converters, the resonant tank in the AC link produces a high-frequency alternating voltage (PRACL) or a high-frequency alternating current (SRACL), in combination with proper operation of the input converter. The switches of both the source-side and the load-side converters are turned on and off when the voltage (PRACL) or the current (SRACL) in the DC link passes through zero, minimizing the switching losses. The switching patterns of the input and output converters should provide the distribution of packets of integral half-cycles of the high-frequency AC link voltage or current among the phases of the input and output converters. The pulse distributions at the input and at the output should exhibit as fundamental components the desired low-frequency voltages or currents. Due to the finite time that must be held between switch commutations (the period of the zero-crossings in the high-frequency AC link), input and output control can only be achieved by discrete-time control methods, like pulse density modulation methods [89]. Conventional PWM control is not applicable.

In a PRACL drive system, the source-side converter must be current-sourced and the output of the converter at the load-side must exhibit a current-sink behaviour. PRACL and SRACL drive systems are dual to each other, so that the source-side converter in a SRACL driver system must be voltage-sourced and the output of the load-side converter must determine the voltage. For motor loads, capacitors must be connected in parallel to provide this behaviour. Since the input and the output as well as the AC link quantities are alternating, the resonant AC link converter requires that all the switches at the input and at the output be bi-directional in current conducting and voltage blocking capability. For each bi-directional switch, two controllable power semiconductor devices must be used, rendering a high number of costly active components. For this reason and due to the complex control, this type of converter is considered uneconomical for general-purpose industrial drive applications in the mediumpower range. modifications in the resonant-switch circuits allow the use of pulse-width modulated control [2]. This type of converter, however, has limited applicability in medium- to high-power electric motor drive systems, due to the higher current stress and associated conduction losses in the resonant switch in ZCS mode, as well as the higher voltage stress in ZVS mode. The main application area for this kind of converter is the field of switch-mode power supplies.

#### 3.1.3 Soft-switching converters for motor drive applications

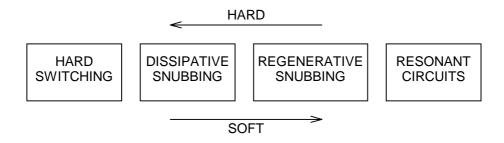

In electric motor drive applications, soft-switching converters are usually classified in three categories, namely *resonant pole* converters, *resonant DC link* converters and *resonant AC link* converters [21]. Detailed descriptions and comparative analysis of these converter types can be found in [22, 89] and will be summarized here. Table 3.1 shows in condensed form the main basic topologies of the above mentioned converter families. There exist many circuit variations in each family, but the placement of the reactive components which produce the resonant transition is what distinguishes a family from the others, and this has been highlighted in Table 3.1. Circuit variations and main characteristics of these converters are discussed further below. The output section of the converters in Table 3.1 is shown in a dashed box for one AC phase only, but in an actual application there would be a number of such sections, depending on the number of machine phases.

Electric motor windings are highly inductive and its input current changes slowly in comparison to converter switching times. Hence, they can be modeled as current sinks. For this reason, it is more convenient to feed them with voltage-source converters (VSC), except for very high power levels above some megawatts, where current-source converters (CSC) may be more economic. The technological reason for that is the better suitability of thyristors as power switches for very high power levels. However, in this case load commutation is used and therefore the switching is done at a very low frequency. In this situation, thyristor CSCs are more attractive, because they are much simpler, and therefore more rugged and reliable at such power levels, than thyris(Fig. 3.2 (a)), if a positive voltage step is applied to the load by closing switches  $S_1$  and  $S_4$ , the load current undergoes a free oscillation. As the current inverts, the corresponding anti-parallel diodes will conduct and the switches  $S_1$  and  $S_4$  can be opened without switching losses. Switches  $S_2$  and  $S_3$  can now be closed, inverting the voltage applied to the load and forcing its current to oscillate continuously, in a sustained resonance. The power flow to the load is controlled by the resonant tank impedance, which in turn depends on the switching frequency. This type of circuit is not very suitable for use with dynamic loads like electrical machines, in particular with SRMs, which exhibit inductances that change with position and current in a wide range, in a highly nonlinear manner. The main application field for this type of converter is induction heating.

Fig. 3.2: Series-resonant (a) and parallel-resonant (b) converters.

## 3.1.2 Resonant-switch converters

A resonant switch is obtained by connecting resonant LC elements to a power semiconductor switch. Some basic resonant switch configurations are shown in Fig. 3.3, but an extensive analysis of many circuit families of this kind can be found in [48]. The operating mode of a resonant-switch converter depends on the placement of the LC elements with respect to the power semiconductor element.